High-Performance 3V Differential LVPECL Clock Buffer | Microchip SY89311UMG-TR

In high-speed digital systems, maintaining signal integrity and precise timing is paramount. The Microchip SY89311UMG-TR stands out as a high-performance differential clock buffer designed to meet the rigorous demands of modern applications. Optimized for 3.3V power supply operation, this device is engineered to distribute ultra-low jitter clock signals across multiple outputs while preserving signal integrity from a single differential input.

The SY89311UMG-TR accepts LVPECL, CML, or LVDS input signals and provides four differential LVPECL outputs. A key feature of this buffer is its exceptional additive phase jitter performance, which is critical for high-speed data communication, networking, and telecommunications equipment where timing errors can significantly impact system performance. With a wide operating frequency range, it supports both very high-speed and lower-frequency clock distribution needs with equal proficiency.

This clock buffer incorporates an internal input termination structure, which simplifies PCB design by eliminating the need for external termination resistors in many applications. This not only saves board space but also reduces component count and overall system cost. Furthermore, the device offers an optional output enable/disable (OE/OD) pin, providing control over the outputs for power management and system testing.

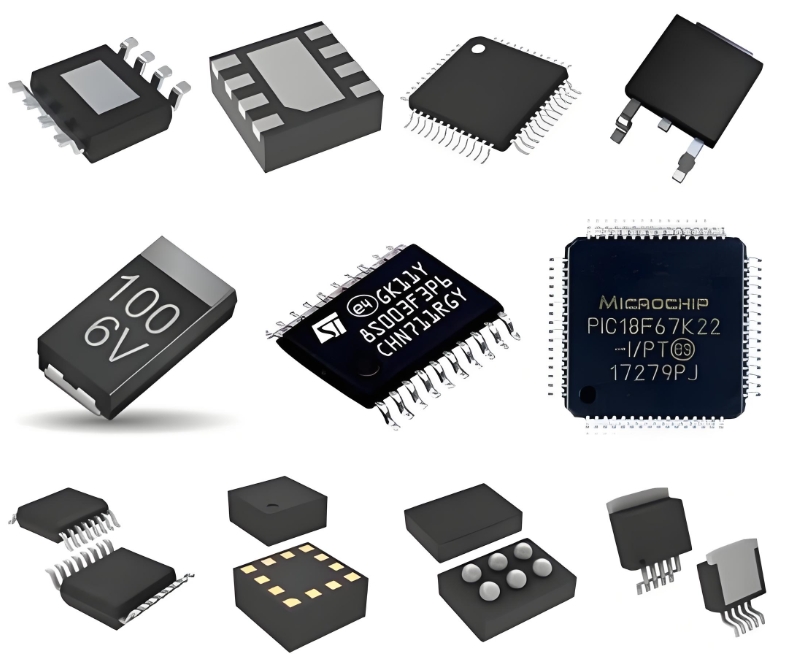

Housed in a compact 16-pin QFN (3mm x 3mm) package, the SY89311UMG-TR is ideal for space-constrained designs. Its industrial temperature range ensures reliable operation across a variety of environmental conditions, making it a versatile choice for a broad spectrum of applications, including routers, switches, servers, and storage area networks.

ICGOOODFIND: The Microchip SY89311UMG-TR is a superior choice for designers seeking a high-performance, low-jitter clock distribution solution. Its integration of internal termination, flexible control, and a small form factor delivers a compelling combination of performance and design simplicity for advanced 3.3V systems.

Keywords: LVPECL, Clock Buffer, Low Jitter, Differential Signaling, 3.3V